- Q.2 a. How integrated resistors are fabricated? Explain diffused resistor method in detail?

- Answer:

ANS 2 (a) The basic technique for obtaining a resistor in integrated circuit is by utilising the bulk resistance of a definid volume q semiconductor region. Diffused Resistor: In this method, resistor is formed in one of the isolated regions of epitaxial layer during base or conitter diffusion common to bipolar transister fabrication This type q visister is very economical. The value q The vesistance depends report the knuface geometry. That is, length, width and report the differed impueity phofike. In this context a very useful quantity sheet resistance is defined as diffused layers are very thim. The resistance of the sheet of material can be written as q a material q Let L g Consider the square LXL sectional area A= LXt thoun in big. The resistance of these that q material resistors can be expressed in terms of the sheet resilitarie Rs and surface dimensions L and w R = P is where ratio 1/10 is called the uspect actio q the surface geometry and is, therefore, The effective number of square contained in the resister. therfore the effective number of square contained ( Uniform in the resister. The base vosister in the range of A=Lt 201 t 300 KN and be Sheet Resistance early fabraled due te medium resistivily p type base regies

**DE56**

b. Why aluminium is usually used for metallization of most ICs? **Answer:**

c. Explain the self aligning property of a polysilicon gate MOSFET Answer:

**Q.3** a. Explain the need for coupling and bypass capacitors in transistor circuits, and draw AC Equivalent circuit of CE amplifier.

Answer:

Avr: 3. The capacitor Ci is used to complethe signal source to the circuit input. Because ci is an open circuit to disect cuerente, is doesnot affect the level of VB. a picitor C, behave as a short cucut for the ac signeds, so that the signal votlage (Vs) appears at the transistor base as showing fig. In this case the signed is said to be ac coupled to the circuit input and ce is

-o<sup>Vec</sup> Coupling copeculis Rì d 33kn j coupling - apaciton Input coupling capacitor referred to as a Rez +12V 11-Cü TROCE Runormally used with all types r []2.7Kn g base circuits, otherwise ≥R2 ISKN T

the circuit bias conditions will be altered. Due to coupling capacities the supply voltage at the transister collector termindel is reduced from Vacto V = Vac \* RL and the collector resistance becomes RC+RL

R- RCIIRL

This has the effect of altering the acciut de load line and of point. The capacitor Cooffies a short circuit to All apartalant ac signals so that there is no feed back from the transistion collector to the base when CB is replaced with a short - au aut, RB, and RB2 appear in pasallel with the air and input and artight respectively. Beared problem of ac degeneration is eliminated syfthe emitter sypas apacter CE

AC Equivalent cuciul · Capaciles behave as short circuls to ac signals so in The ac equivalent circuit for a transister circuit all capaciters must be replaced with short incits Seconse the dc supply voltage is not affected by The ac signals those all power supplies have large value capacillass at the artput tarminels and these well offer schoots arcuits to ac signals. Substituting short arauts in place of all the pomer supply and all apacitos in the araut below big gives ac equivalent circuit

. y RL is present, it appears in pasallel R, RL wisth Rc in The ac ZRC equivalent ai and

Poner supply and capacitors behave as a what - circuits

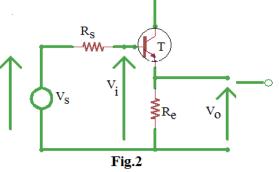

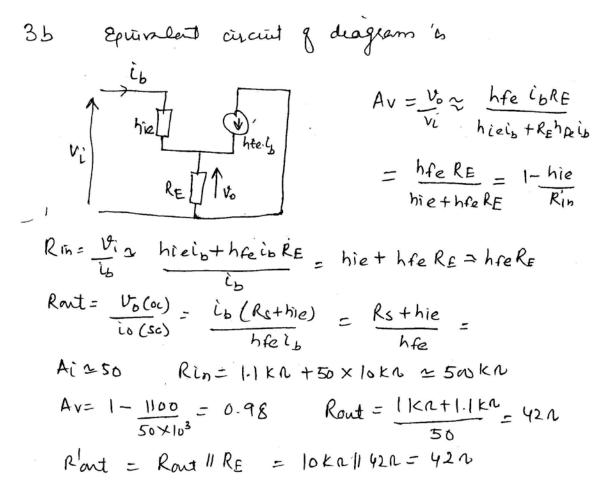

b. Use the simplified h-parameter model to derive equations for the current gain  $A_i$ , the input impedance  $R_{in}$ , the gain  $A_v$  and the output impedance  $R_{out}$  for the emitter follower circuit shown in Fig.2. Calculate the value of these parameters, assuming  $h_{ie} = 1100\Omega$ ,  $R_e = 10 \text{ K}\Omega$ ,  $h_{fe} = 50$  and  $R_s = 1k\Omega$

Answer:

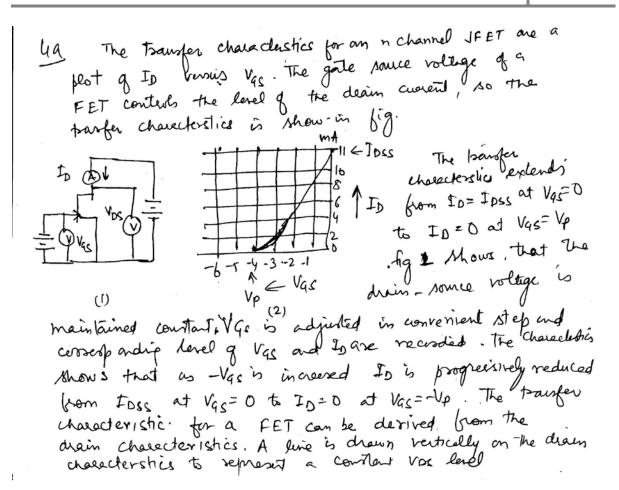

Q.4 a. Draw and explain the transfer characteristics of JFET. List the advantages of JFET.

Answer:

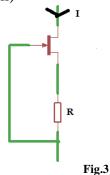

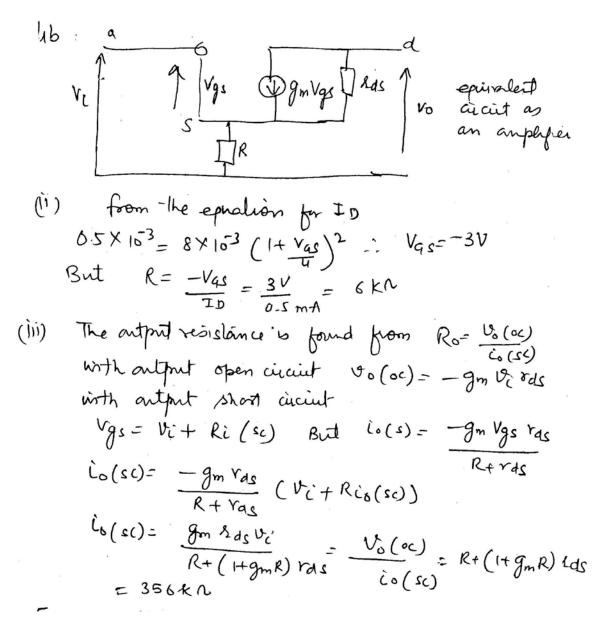

b. The constant current circuit shown in Fig.3 uses a JFET whose operation is described by the equation

$I_D = I_{DSS}(1-V_{GS}/V_P)^2$ ,  $I_{DSS} = 8 \text{ mA}$  and  $V_p = 4 \text{ V}$

- (i) Draw the equivalent circuit as an amplifier

- (ii) Calculate the required value of R to give a current of 0.5 mA

- (iii) If the FET drain- source resistance  $r_{ds}$  is equal to 50 K $\Omega$  at  $I_D = 0.5$  mA, determine the incremental resistance of the circuit for the value of R calculated in (ii)

Answer:

Q.5 a. Draw and explain the circuit of complementary emitter follower. Answer: INO BJTS connected to function as anniter follower relected to have similes parameters, so they are complementary transistors. The circuit is themed as a complementary emitter follower Answeglerta complementary emitter follower Answeglerta complementary emitter follower basies as showin for applied simultaneously to both dance basies as showin for Transistor Q: conducts during the positive half cycle y the signal and it pulls the artput voltage up to follow the input. During this time Q2 base-emitted tinction is reverse blased. For the duction of the negative Rely cycle of the import Q1 base emitter function is reversed and Q2 conducts, pulling the output down to bollow the import. Thus, the complementary emittee bollower is a large scale circuit with the low august mpedance. Another advantage is, this circuit does not reprire toanformer. This saves an weight and cost  $\frac{1}{\sqrt{2}}$   $\frac{p_{np}}{\sqrt{2}}$   $\frac{q_{n}}{\sqrt{2}}$   $\frac{1}{\sqrt{2}}$

b. Draw the circuits of opto-coupler with SCR and Triac and briefly explain these circuits.

Answer:

(b) q(c) SCR q triac type are a light activated SCR and light activated triac type. They are used will They gre used with where thigh electrical the kind of conterf circuits Isolation between the triggering circuit and the control device is an additional reputiement CTR doesnot apply to scR and Triac autput stages instead, the LED the thyrister trigger ( needed to S 2 current interest. C 10 **0**5 20 30

c. Show that maximum collector efficiency of class A transformer coupled power amplifier is 50%.

## Answer:

**Q.6** a. What is the need of negative feedback in OPAMP? **Answer:**

In op-oup is almost always operated with ne feedback is a part of the autput is fedback in phase opposition to the input. With negative feedback, the voltage gain can be reduced and controlled So that op-and can function as linear aughties. In addition to providing a conterlled and stable gain, negative feedback Jaho provides for conterf of the part and artput impedances and imperfier bandwith Ki RF -o Vart b. Define the following parameter and give their values for IC 723 (i) Input bias current (ii) CMMR (iii) Output resistance (iv) Input offset voltage Answer: (b) [0) 10 The average of the cuerent's entering into (-) uput and (+) input terminals q an op-anp. Its value is 500 mA for 741C CMMR is typically godB. (6) (C) It is the resistance between the output terminal of the op-amp and the ground. It is 750 for the 741 cop-anp (d) It is the voltage that must be applied between the mport terminals of an op-any to mility the autput for 741C, the maximum value is 6m V

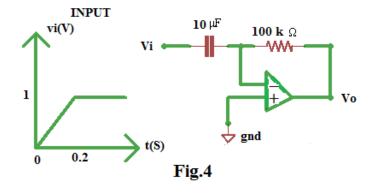

- c. For the differentiator circuit shown in Fig.4, find:

- (i) the expression for the output voltage

- (ii) the output voltage for the given input.

Answer:

citration R2

1) for the differentiation, the autput voltage is given by

Vo = -Rc dvi = -(look 1. × 10. HF) dvi

The dvi

The dvi = -(look 1. × 10. HF) dvi

The dvi

The input voltage is straight line between 6 for 2 sec

the autput voltage is

$$90 = -dvi = (1-0) = -5V$$

Italefore between oto 0.25 the autput voltage is constant

at -5V for t70.25 the input is constant so that

autput voltage is 2 ero.  $0 = -5V$

**Q.7** a. Draw and explain Sample and Hold circuit using OPAMP. Draw input and output waveform of the circuit.

Answer:

Ans 7(a) A sample and hold circuit samples an upont signed and holds on to its last sampled value untill the mont is sampled again. The circuit show in fig n channel E- mosfiet Control rollage

The n channel E- MOSFET works as a switch and is controlled by the control rollage ve and the capacitor C stores the charge. The analog signal vi to be sampled is applied to the dears of E - MOSFET and the control voltage us is applied to its gate when ve's positue the E-MUSFET tuens and the capacities C changes to The instantaneous value q input vi usth a time constant [Rot & ps (on)] C. there to is the autput renstance of the voltage bollower AI and ros (on) is the resistance give MOSFET When On. Thus the wont vollage vi appears across the capacitor C and then at the artput through the voltage follower A2. When VC is zero The E MOSFET 15 off. The capacities C is now bacing the high input impedance q the voltage follower Az and hence cannot dischalle The capacitar holds the vollage across it. The line period TH of ve during which The boltage across the capacitor is held constant is called hold period OKTS >K-TH-7

and artput ware

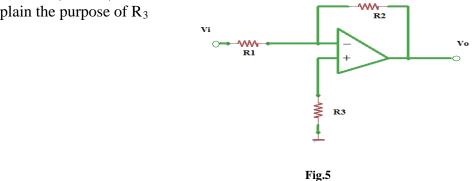

b. For the circuit shown in the Fig.5 assuming that the input current is negligible, show that  $v_0/v_i = f(R_2, R_1, A)$  and that it may be approximately to  $v_0/v_i = -(R_2/R_1)$ . Explain the purpose of  $R_3$

Answer:

7(b) Let the non-investing input be vg. current in

$$R_1$$

be  $i_{1,1}$  and the current in  $R_2$  be  $i_2$

$\therefore i_1 = \frac{V_1 - V_9}{R_1}$  and  $i_2 = \frac{V_9 - V_0}{R_2}$

But since amplifier imput current is zero  $i_1 \approx i_2$

$-\frac{V_1 - V_9}{R_1} = \frac{V_9 - V_0}{R_2}$

Now  $V_0 = -AV_9$ , where  $A$  is the openloop gains

$\frac{V_1 + V_0}{R_1} = -\left(\frac{V_0 + V_0}{A}\right)$

$-\frac{V_0}{V_1} = \frac{R_2}{R_1}\left(\frac{1 + R_1 + R_2}{AR_1}\right)$  for large value of  $\frac{V_0}{V_0} \approx \frac{R_1}{R_1}$

The purpose  $R_3$  is to reduce the effect  $g$  input

offset voltage due to input bias current

$-\frac{V_1 - R_2}{R_1 + R_2}$

**Q.8** a. What are the applications of comparators? Explain the operation of zero crossing detector.

ANALOG ELECTRONICS DEC 2013

Answer:

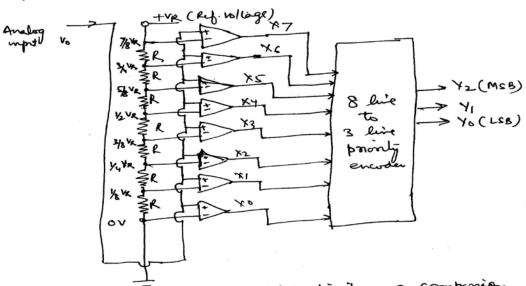

Q.9 Write Short notes on any **<u>TWO</u>** of the following: (i) 723 general purpose voltage regulator (ii) Flash type A/D convertor (iii) IC voltage regulator

Answer:

96) anevent Boosling. The maximum avent that 723 IC regulator dan provide is 140 mm. which & not sufficient for many applications and it is possible to boost the current level simply by adding a boost Transister of to the voltage regulator. The collector aurent of the pan transister Q, comes from the Unregulated de kupply The output current from Vo terminal deires the base of the

9(b) It is the fastert and most expensive type ADC 3 bit A/D converter shown in big connet of a resistive dwiden network, & op-amp comparator and shire to 3 encoder

At social each node q'the resistive divider, a compansion voltage is available. Since all the resistors are q epief

Value, the voltage levels available at the nodes are equally divided between the ref. voltage VR and ground The purpose of the circuit is to compare The analog upot voltage Va with each of the node voltages. The circuit has the advantage of high speed as the conversion take place simultaneously rather than sequentially and disadvantage that the number of comparators reputed almost southles for each added bit. For barge value of n, the mose complex is the pauly encoder

## **Text Books**

1. Electronic Devices and Circuits, Fourth Edition, David A Bell, PHI (2006).

2. Linear Integrated Circuits, Revised Second Edition, D. Roy Choudhury, Shail B. Jain, New Age International Publishers.